任意拆开一套现代电子产品,我们基本上都会看到印刷电路板(printed circuit board,简称 PCB)的身影。仔细观察这个常见的组件,你可以看到它表面上布设了很多条铜线。这些导线可以利用电沉积工艺进行印制,因为这项工艺能够通过电化学反应改变器件表面。为了提高面向电路板制造的电沉积技术,工程师可以借助数值建模。

利用电沉积制造印刷电路板

简而言之,电沉积是一种使用其他材料给基底上涂层的电化学过程。这种工艺兼具装饰功能和实用功能,可用于各种不同领域,如电子、采矿和纳米技术。电镀属于电沉积的一种,主要用途是电路板制造。

PCB通常由一层或多层铜制成,这些铜沉积在非导电基底之上或之间。铜层被分割成导线或在 PCB 中传输信号的走线。在印制这些图形线路时,工程师会将铜电镀到电路板上的微腔中。

PCB 实例。图片来自 AB Open。在CC BY 2.0 许可下使用,通过Flickr Creative Commons分享。

利用电镀工艺制造 PCB 需要克服许多难题。举例来说,如果 PCB 表面的镀铜速率发生变化,可能会导致性能问题甚至是设备故障。为了找到并消除电镀过程中的问题,工程师可以使用COMSOL Multiphysics® 软件和附加的“电镀模块”。

分析电路板沟槽中铜的电化学沉积过程

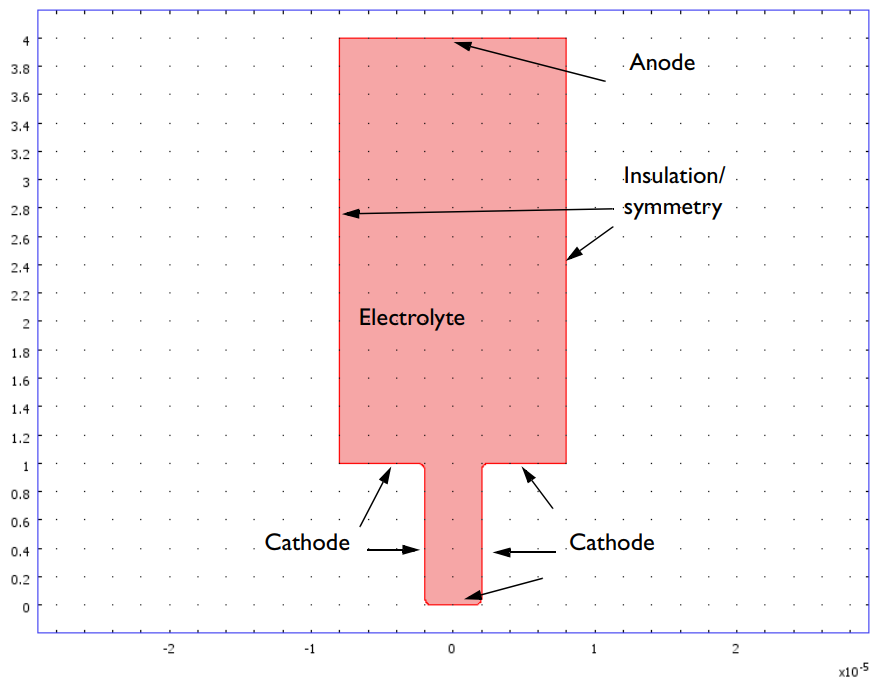

本文的示例模拟了带细小沟槽或微腔的电路板上的铜电化学沉积过程。在恒电位控制下的实验室电池充当了电镀电池,阳极与阴极相互靠近。沉积发生后,阴极和阳极的边界开始移动,因此仿真本质上依赖于时间。另外,阴极表面的镀铜沉积速率是不均匀的。

此模型是电沉积的基准模型,它充分说明了 COMSOL® 软件在求解涉及变形几何的电化学问题方面的强大能力。此例使用变形几何分析了电镀过程及空腔对电镀结果的影响。通过使用变形几何,工程师能够研究在电镀过程中阴极边界的生长过程。

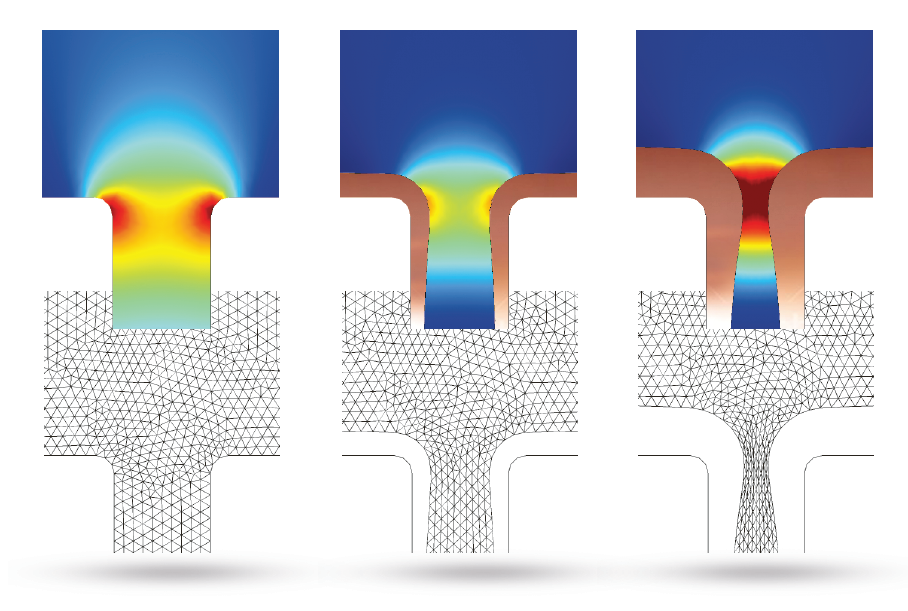

铜沉积的几何模型。垂直的壁表示主电极的图案,壁为绝缘体。

要求解此问题,工程师可以使用内置的任意拉格朗日-欧拉(ALE)方法,该方法可以根据底层物理场预测物体的变形或位移。借助 ALE 方法,工程师能够正确地研究高精度电沉积模型中的沉积物形状。

如果您想了解更多有关模型设置的信息,包括 E. Mattsson 和 J.O’M. Bockris 创造的基础模型,请查看此处的模型文档。

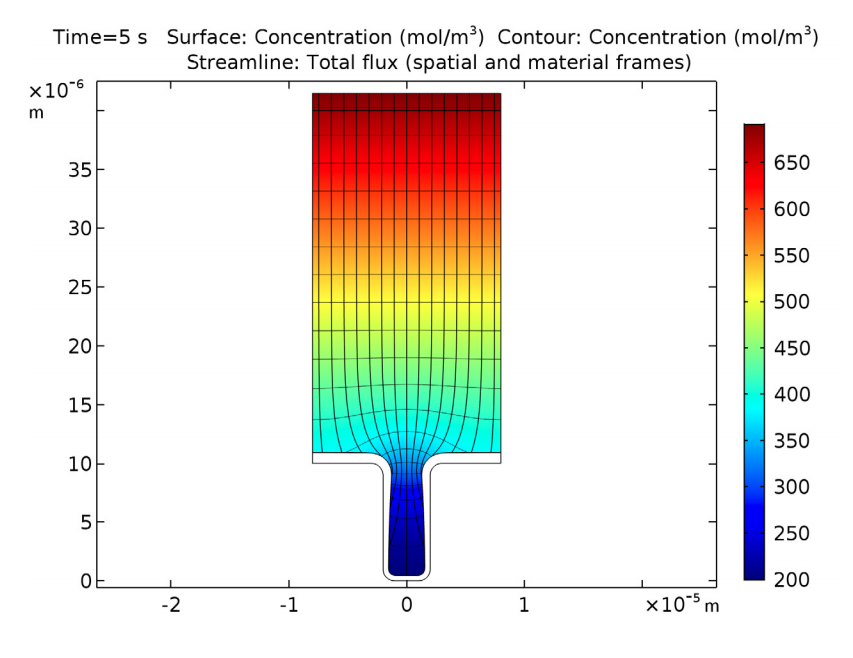

铜电化学沉积过程的仿真结果

下面,我们查看 5 秒钟之后铜的沉积过程。此时,整个电池中的铜离子浓度差异巨大。这些差异最终可能导致电池内产生自由对流,不过基准模型没有考虑这一点。我们可以看到沟槽出口开始变窄,这是由于铜沉积厚度不均匀而导致的。

铜离子浓度、等电位线、电流密度流线以及阴极和阳极位移。模型沿电池中间的垂直线呈轴对称。这是个好现象,因为结果不对称说明网格分辨率较差。

下方结果表明,随时间推移,沟槽顶端持续变窄。这会破坏沉积质量,因为被捕获的电解质可能导致电路板组件遭受腐蚀。

图片(上排)和动画(下排)显示铜材料随时间的沉积过程。图片也突出演示了用于求解此示例的移动网格。

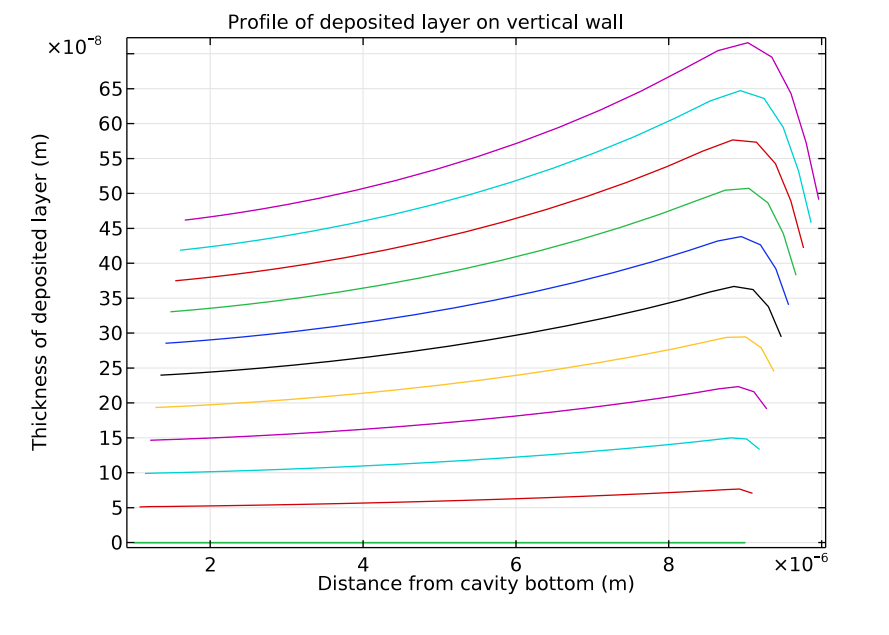

下一张图研究了垂直阴极表面上的沉积层厚度。这张绘图从另一个角度展示了不均匀沉积发生的过程。根本原因在于电流密度分布不均匀,另外,沿腔深度的铜离子不断被消耗,从而加剧不均匀分布。

沿垂直阴极边界的沉积层厚度。图中的每条线表示在 0.4~4.4 秒范围每 0.4 秒的增量。

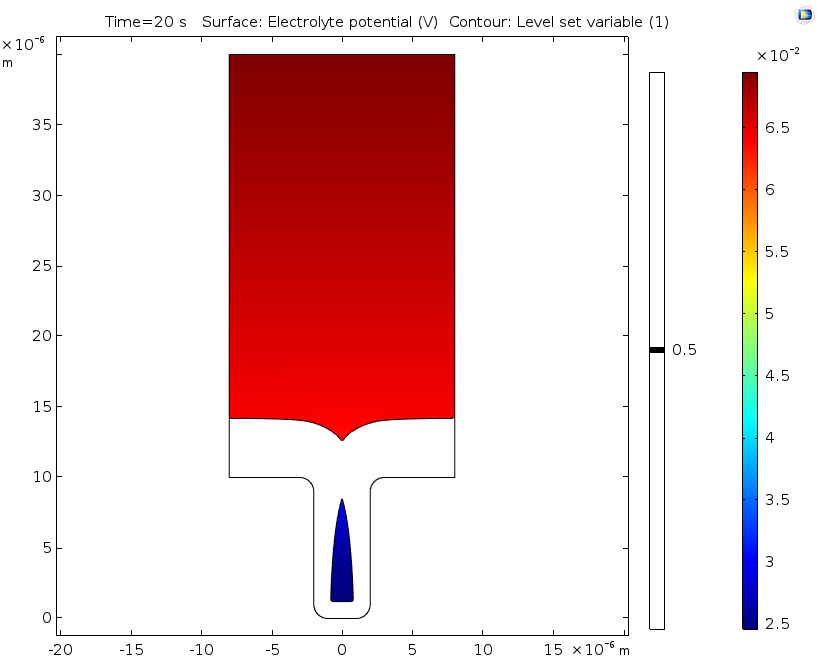

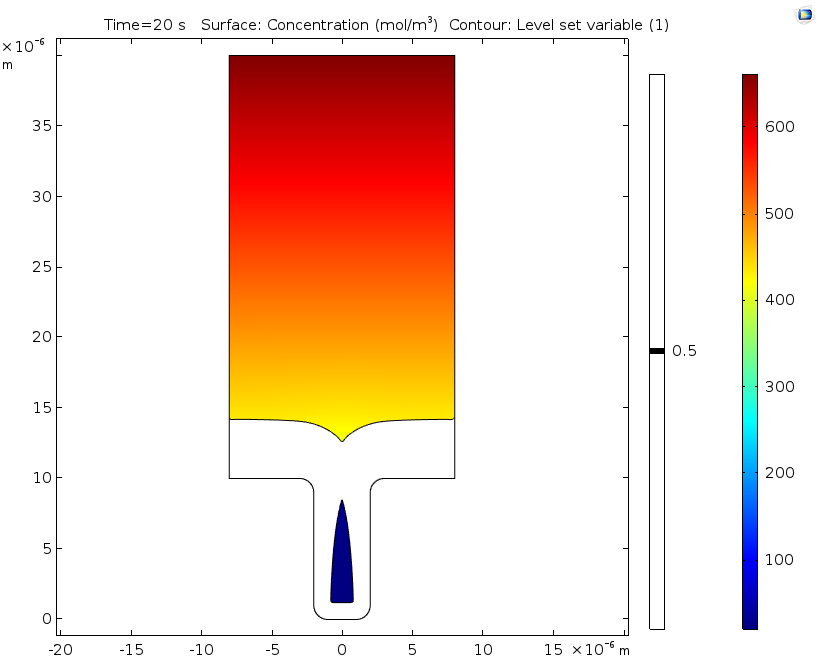

如果需要的话,工程师可以将 ALE 法更换为水平集方法,从而延长这项分析的研究时间,如链接案例所示。这样,我们就可以分析微腔形成之后 的沉积过程,因为水平集方法能够研究拓扑变化。扩展分析表明,不均匀沉积导致形成具有潜在危害的空腔或空隙。与上一轮的 ALE 结果一样,铜离子浓度也显示出了明显变化。

沉积发生了 20 秒后,水平集变量为 0.5 的等值线对应的电解质电位(左)和铜离子浓度(右)。

总而言之,上述结果表明,目前的设计可能会损害沉积层的质量,导致腐蚀和材料浪费。通过数值建模确定这些潜在问题后,工程师就找到了改进设计的突破口……

仿真助力优化铜电化学沉积工艺

借助类似的模型,工程师可以准确地分析电沉积过程,并测试不同的操作参数、施加电位和沉积表面的几何形状。通过这种方式,他们可以找到最优的电沉积参数,提高沉积层的均匀性,从而制造出高质量的产品。

本文中的模型可用作实现这些目标的起点模型。工程师可以根据具体需求来改造此基础模型,例如引入其他离子的影响和测试更多不同的复杂几何。如需自己动手尝试,请单击下方按钮进入“案例下载”页面,如果您拥有有效的软件许可证和 COMSOL Access 帐户,即可此下载相关的 MPH 文件和教程文档。

评论 (0)