COMSOL News

多物理场仿真杂志:IEEE 特刊

突破芯片密度的限制

Derek Bassett and Michael CarcasiTokyo Electron America

Austin, TX

芯片制造商一直在坚持遵守摩尔定律,它规定了自 1965 年起,出于经济考虑能放置在集成电路上的晶体管数量每年翻一倍。然而,由于晶体管的数量增加,制造集成电路的过程(也叫光刻)变得更加困难。每个装置都需要大约 200 个清洁和光刻步骤,而且此过程一旦出现故障就可能斥资数百万美元。

Tokyo Electron America (TEL) 是一家制造集成电路处理重要工具的生产商,他们使用仿真来了解一种称为图形倒线的故障类型。图形倒线会在两个特征之间的清洁流体蒸发时发生,而在蒸发过程中表面张力发生变化会导致特征弯曲。理想情况下,这些特征会恢复正常形态,但有时它们发生永久变形。

TEL 的研究人员使用 COMSOL Multiphysics 软件创建了一个二维结构力学模型,它基于以表面张力为边界条件的一系列稳态计算。他们将这些结果与文献数据进行对比,发现该模型精确地预测了倒线临界纵横比。

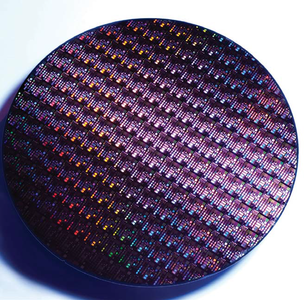

经历多重光刻步骤的 300 mm 图样化半导体晶片。

经历多重光刻步骤的 300 mm 图样化半导体晶片。

下载

- Tokyo_Electron_MS2013.pdf - 2.51MB